Osnovi dizajniranja Gejt drajvera

Igbt se dovodi u stanje provodljivosti, kada se prikladan napon (obično +15V) dovede na gejt tranzistora, a struja je blokirana ako je Vge ispod napona držanja ( generalno je Vge(th) ispod 0V). Ovo su idealni uslovi I pod njima napon između kolektora I emitera Vce bi trebao biti 0V, te su I gubici pri prekidanju takođe nula, uzimajući u obzir da Igbt tranzistor radi u prekidačkom modu, a ne kao linearni pojačavač.

Naravno, u realnoj situaciji ovo nije moguće, tako da se kvalitetan Igbt približava ovom stanju, te se pri izboru samog tranzistora treba potruditi da isti što bliže zadovoljava ove karakteristike. Da bi se realizovale najbolje perfomanse Igbt-a posebna pažnja se posvećuje kontroli gejta (Gate driver), a osnovni parametri su …Vgg+ (positive gate bias voltage), Rg, maksimalna struja gejta (Ig), kao I samo okruženje eksternih komponenti I na kraju sama snaga drajvera. Da bi se konstruisao kvalitetan drajver ove parametre je neizbežno uzeti u obzir I apsolutno ih razumeti kao I karakteristike samog Igb tranzistora.

Vrednost Vgg+ je u direktnoj vezi sa gubicima u “On” stanju I brzinom prekidanja, dok je vrednost otponika Rg u direktnoj vezi sa prekidačkim karakteristikama. To znači, da ako snaga samog drajvera ili napajanje kapaciteta Ig nije dovoljna, onda vrednosti Vgg+ I Rg postaju beznačajne. U isto vreme treba posvetiti pažnju I samom okruženju gejt drajvera da bi se izbeglo indukovano isključenje zbog dv/dt. O ovim parametrima ćemo govoriti u nastavku, a bazirano na Sl.4 iz prethodnog teksta. Potrebno je znati da elektronske komponente sa boljim karakteristikama u osnovi imaju manje rasipanje snage, što je opet u direktnoj vezi sa cenom, veličinom I iskorišćenjem celog sistema.

A. VGG+

Vgg+ je napon između gejta i emitera tokom provodljivosti, i to je jedan od najvažnijih parametara u dizajniranju gejt drajvera. Vrednost Vgg+ mora biti ustanovljena uzimajući u obzir podatke iz tabela proizvođača, a to su: struja, napon, SOA dijagram, maksimalne vrednosti Ic i Vce, vrednost Tf te međusobnu vezu ovih prametara.

a. Minimalna i maksimalna vrednost

Maksimalna vrednost Vgg+ je određena limitom izolacije gejt oksida. Ako napon između gejta i emitera pređe gornju granicu to dovodi do uništenja gejt oksida. Sa tim u vezi napon Vgg+ u aplikacijama mora biti manji od njegove maksimalne vrednosti. Minimalna vrednost Vgg+ je najniža vrednost u granicama zasićenja tokom provođenja.

b. Vgg+ efekat na „Stanje“

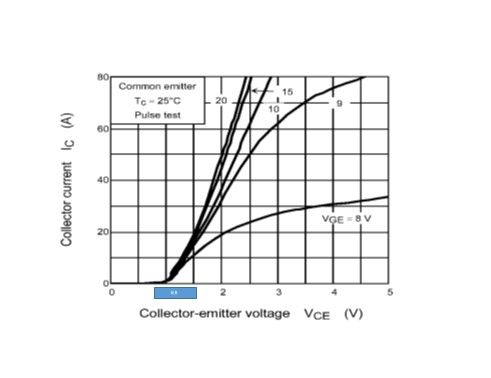

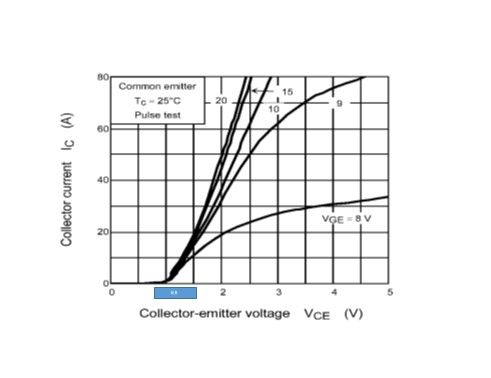

Za istu vrednost struje kolektora (Ic), napon zasićenja Vce je u obrnutoj vezi sa vrednošću napona Vgg+. Za manju vrednost Vgg+, kanal između n+ sloja i n-strujećeg sloja postaji tanji, i otpor u kanalu se povećava. Pad napona u n- regiji je očigledno manji nego kod Mosfet tranzistora. Kao posledica otpor u kanalu raste opadanjem napona između kolektora i emitera tokom stanja „On“. Imajući u vidu navedene činjenice, Vge opada tokom prekidačkog ciklusa, kanal postaje tanji povećavanjem otpora. Ovo dovodi do povećanja napona zasićenja između kolektora i emitera (Vce(sat)), te gubici u stanju „On“ postaju veći. Ako to znamo onda bi bilo bolje koristiti najveću moguću vrednost Vgg+. U aplikacijama gde su gubici u „On“ stanju dosta veći, veoma je važno povećati vrednost Vgg+, te smanjiti Vce(sat) kako bi se smanjio gubitak provodljivosti.Kao primer na sl.5 je prikazana kriva za Toshibin GT40QR21 Igbt. Izvinjavamo se zbog loše rezolucije (slika je preuzeta iz PDFa proizvođača).

Sl.5 GT40QR21 Tipične izlazne karakteristike

c. Efekti na „Turn-on“ proces

Uopšteno, dok Vgg+, ( Vgg+ - Vge(th)) raste, vreme prekidanja se smanjuje i samim tim se smanjuju prekidački gubici. Za posledicu imamo veću struju koja teče kroz gejt tokom „Turn-on“ ciklusa, brže punjenje Cge, i napon Vge rapidno raste, što vodi ka bržem porastu struje Ic. Pogledajte sledeću jednačinu; Ig = (Vgg+ - Vge) / Rg. Iz nje možemo zaključiti da se struja gejta povećava sa rastom Vgg+, što vodi ka povećanju dIc/dt Pošto su pokrivajuće karakteristike FWD (freewheeling diode) na suprotnoj strani funkcija odnosa dIc/dt, oporavljajući strujni pik FWD-e (što je Igbt-ova prekostrujna karakteristika, a pokazana na slici br.3 u prošlom tekstu), zatim prenapon od FWD-e i dVce/dt su uzrokovani promenama u dIc/dt. Kada dIc/dt raste, prekostrujni talas Igbt-a i prenaponski stres FWD-e rastu, dok to takođe izaziva porast u padu dVce/dt Igbt-a i porast dVce/dt diodnog napona na suprotnoj strani. Velika vrednost dIc/dt i dVce/dt je indikator brzine prekidanja, ili da su prekidački gubici mali, što bi mogla biti prednost, ali iz perspektive limitiranja EMI šumova, neophodno je setovati gornju granicu. Fundamentalni metod da se limitira prekostrujni talas Ic je da se izabere Igbt čija dioda ima bolje pokrivajuće karakteristike (principijelno veću brzinu rada te duže vreme opstanka u kratkom spoju). U svakom slučaju, posle izbora pravog Igb tranzistora, te setup-ovanja, struja Ic se može kontrolisati ispod deklarisane granice redukujući Vgg+, ili povećanjem otpora Rg. Igbt-ov prekostrujni talas i FWD-ni prenapon na drugoj strani takođe može redukovati dIc/dt limitiranjem Vgg+ ili povećanjem Rg. Prilikom odabira Igbt-a sa integrisanom diodom (co-pak Igbt), prenaponski pik ne sme preći deklarisani napon diode (taj podatak se nalazi u PDF-u pod specifikacijama).

d. Efekat na sposobnost izdržljivosti kratkog spoja

Igbt-ova izdržljivost kratkog spoja se može takođe regulisati sa Vgg+. Manji Vgg+ znači manji granični napon tokom trajanja kratkog spoja, te manje rasipanje toplote. Drugim rečima vreme izdržljivosti u kratkom spoju raste. Uzimajući u obzir ove karakteristike zaštita od kratkog spoja može biti osmišljena sa Vge. Dakle, da se zaključiti, da se sa rastom u Vgg+ mora pretpostaviti povećanje gubitaka u „On“ stanju. Serija RUF tranzistora (Fairchild) mogu podneti kratak spoj oko 10uS.

e. Efekti na „Turn-of“ proces

Kao što su karakteristike Igbt-a u „Turn-on“ ciklusu uzrokovane sa Vgg+, tako su i „Turn-of“ karakteristike uzrokovane sa Vgg- (negative gate bias voltage). U svakom slučaju strujni rep koji se pojavljuje, dolazi od karakteristika BJT tranzistora Igbt-a, koji je prirodno integrisan u Igbt-u, te ne može biti kontrolisan spolja sa Vgg-. Dok vrednost Vgg- se povećava, prekidački gubici struje kolektora Ic u „Turn-of“ ciklusu se smanjuju. Dok se vrednost Vgg- povećava, di/dt struje kolektora(Ic) raste,te se di/dt struje Id povećava za isti iznos. Parazitni induktivitet i di/dt od Id su dodati na Vdc(sl.4 iz prošlog teksta) po sledećoj jednacini V=Ls*di/dt. Dok apsolutna vrednost Vgg raste, dIc/dt i dVce/dt raste, i takođe dok dIc/dt raste i prenapon od Vce raste. Vrednost pika ovog prenapona ne sme preći Igbt-ovu maksimalno deklarisanu granicu, tako da redukcijom vrednosti Vgg- možemo kontrolisati gornju granicu. Sa druge strane ako je vrednost Vgg- povećana, mogućnost od „prostrela“ dV/dt je redukovana (pogledaj pod Rg Efekat na Turn-on stanje, pojašnjeno u sledećem pasusu).

B. RG

a. Efekti na „Turn-on“ proces

Serijski otpor(Rg), koji je konektovan na gejt Igb tranzistora, je parametar koji značajno utiče na prekidački oblik signala. Kada Rg smanjuje vrednost, dIc/dt i dVce/dt raste u oba prekidačka ciklusa(Turn-on i Turn-of), te se prekidački gubici smanjuju. Postoji jedna važna prednost kad je Rg manji, a to je dokazan dV/dt imunitet na šum(Opasni udarni napon na gejt Igbt-a izazvan Millerovim efektom ili dV/dt šumom znači da se može izbeći indukovano uključenje). Kada se jedna strana Igbt-a u polumostu uključi, tada FWD na Igbt-u na drugoj strani pokriva povratni napon te postoji dV/dt. Ovaj dV/dt trenutno provodi Igbt na drugoj strani. S obzirom da je parazitski kapacitet između kolektora i gejta Ccg na drugoj strani napunjen sa dVce/dt na Igbt-u na drugoj strani, tada ova struja teče ka gejtu kako bi se smanjio napon. Ovo na trenutak dovodi do prelaska naponskog praga gejta te stavlja Igbt u stanje provodnosti. Ova pojava se zove dV/dt prostrel. Ovo izaziva nepotrebne gubitke, ali redukcijom otpora gejta Rg opada vrednost redukcije napona na kraju. Takođe efektivan način je povećanje vrednosti Vgg-, jer to ograničava mogućnost napona gejta Igbt-a da raste preko Vge(th). Uprkos ovim prednostima, minimalna vrednost Rg je ograničena, i to karakteristikama oporavka FWD-e od Igbt-a na suprotnoj strani. dI/dt i dV/dt stres FWD-ena drugoj strani se menja sa vrednošću Rg usled teškog prekidanja induktivnog opterećenja. Ako je dIc/dt veća, onda se povećava i mogućnost oscilovanja (verovatno su iskusniji serviseri aparata za zavarivanje primetili ovu pojavu). Kada dIc/dt raste, takođe raste i dVce/dt. Pošto dIc/dt postaje veći, veća je i mogućnost naponskog prostrela (dV/dt) na Igbt-u sa druge strane. Pod ovim okolnistima, moraju se uzeti u obzir prekidački gubici u „Turn-on“ ciklusu, i povećati Rg da se ograniči stres na FWD-i.

b. Efekti na „Turn-off“ proces

Iako je Rg mali, on ima isti efekat kao i povećanje Vgg-. Sa povećanjem Rg, „Turn-off“ vreme padanja raste, tako da se povećavaju prekidački gubici. U svakom slučaju, ovi gubici su manji nego tokom „Turn-on“ ciklusa. Kako je struja kolektora Ic podeljena među Mosfet i PNP tranzistorima, samo struja Mosfet-a može biti kontrolisana tokom „Turn-off“ ciklusa. Iz perspektive od dV/dt imunosti na šum, dV/dt nepravilnosti od Igbt-a na drugoj strani mogu biti redukovane tokom „Turn-on“ ako je vrednost Rg veliki. Nasuprot „off“ stanju, raste mogućnost od dV/dt prostrela Igbt-a tokom „Turn-on“ ciklusa. Uzimajući sve gore navedeno u obzir, ako koristimo različite vrednosti Rg za „turn-on“ i „Turn-off“ stanja, vrednost otpora može se korigovati prema potrebama ova dva stanja.

Nadamo se da ste uživali, ostanite sa nama i daljede ćemo pisati o dizajniranju gejt drajvera, te pojasniti potrebnu snagu gejt drajvera, fizičkom okruženju gejt drajvera, stabilizacionom kondenzatoru izvora napajanja, problemu izolacije gejt drajvera kao i o obrascu ožičenja.

Naše usluge su bazirane na uverenju da su potrebe korisnika najbitnije. Mi smo se obavezali da ćemo te potrebe i poštovati. Pozdravljamo priliku da zaradimo vaše poverenje, te da vam omogućimo najbolji servis aparata za zavarivanje po najpovoljnijim cenama.

Naše usluge su bazirane na uverenju da su potrebe korisnika najbitnije. Mi smo se obavezali da ćemo te potrebe i poštovati. Pozdravljamo priliku da zaradimo vaše poverenje, te da vam omogućimo najbolji servis aparata za zavarivanje po najpovoljnijim cenama.